Electrical resistive and thermally conductive nano-coatings will enable lower cost electronics manufacturing and enhance the ultimate properties of lattice materials for ultra-high temperature applications

Problem

Advanced nano-coatings for high-speed applications aim to develop low-cost, high thermal conductivity, high electrical resistivity coatings for thermal management in high-performance computing applications. The demand for increasing computation results in the need for superior thermal management solutions. Data processing generates heat through joule heating in conductive traces from which inadequate thermal management results in ‘thermal throttling’, and improving thermal management enables better performance. Thermal and electrical management in high-speed platforms will require advanced, lightweight solutions. Thermal management currently requires dependence on exquisite components like synthetic diamond.

Objective

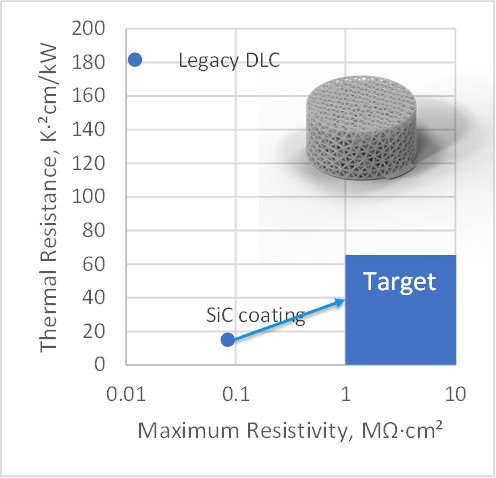

The purpose of this project is to identify thermally conductive, electrical insulative (TCEI) thin-film coating solutions for heat spreader applications to increase the computational potential of today’s high-performance military and consumer electronics. The program aims to identify surrogate electronics systems for highspeed platforms where nano-coatings can advance thermal management performance. The project seeks to achieve 1 MΩ of resistance on a 12 mm x 12 mm square on copper coupons and a total coating thickness of 15 microns before coating failure. Finally, this project seeks to identify partners in electronics manufacturing to accelerate the production of high-speed processing components that currently rely on synthetic diamond for thermal management to benefit the Department of Defense (DoD).

Technical Approach

United Protective Technologies (UPT) will examine various deposition parameters of the previously developed and completed amorphous silicon carbonitride process that provided the best thermal conductivity and electrical resistance results. Fifty 30x30x1.6mm C110 copper test coupons will be prepared for coatings. UPT’s current thermal conductivity measurement system will be upgraded to a Thermal Electrical Resistance Measurement System (ThERMS) allowing measurement of thermal and electrical resistance of coated samples simultaneously. Coating stress will be measured via a thin film stress measurement system. Silicon wafers will be used to develop high-thickness, low-stress amorphous silicon carbonitride coatings. Temperature, flow rate, and deposition rate will be evaluated to determine favorable high thickness and low stress. With approved coating adhesion after scratch testing, the coupons will be coated and tested with the thermal conductivity measurement system and compared against the baseline collected in Phase I to isolate the thermal resistance of the coating. Electrical resistance will be tested over a 12x12mm square area in hopes of achieving a value higher than 1 MΩ and a thermal resistance less than 60 K-cm/kW. UPT will also provide General Lattice with both thin film coating depositions and support for applications and testing of AM lattice structures with these nano-coatings.

Project Participants

Project Principal

Other Project Participants

- General Lattice

Public Participants

- U.S. Department of Defense